UltraSPARC - UltraSPARC

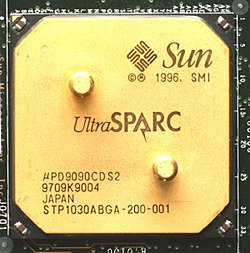

Um microprocessador 200 MHz UltraSPARC

| |

| Produzido | De 1995 a 1997 |

|---|---|

| Projetado por | Sun Microsystems |

| Max. CPU clock | 143 MHz a 200 MHz |

| Conjunto de instruções | SPARC V9 |

| Cores | 1 |

| Antecessor | SuperSPARC II |

| Sucessor | UltraSPARC II |

O UltraSPARC é um microprocessador desenvolvido pela Sun Microsystems e fabricado pela Texas Instruments , introduzido em meados de 1995. É o primeiro microprocessador de Sol para implementar a 64 bits SPARC V9 conjunto de instruções (ISA). Marc Tremblay foi uma co-microarchitect.

Conteúdo

microarquitetura

O UltraSPARC é um de quatro questão superscalar microprocessador que executa as instruções na in-fim . Tem um número inteiro de nove fase oleoduto .

unidades funcionais

As unidades de execução foram simplificadas em relação ao SuperSPARC para alcançar freqüências de clock mais altas - um exemplo de uma simplificação é que os ALUs não estavam em cascata, ao contrário do SuperSPARC, para evitar restringir freqüência de clock.

O inteiro arquivo de registro tem 32 entradas de 64 bits. Como o SPARC ISA usa janelas de registradores , dos quais o UltraSPARC tem oito, o número real de registros é 144. O arquivo de registro tem sete leitura e três portas de escrita. O arquivo de registro inteiro fornece registros de dois unidade lógica e aritmética e da unidade de carga / loja. As duas ALUs tanto pode executar a aritmética, lógica e mudar instruções, mas apenas um pode executar multiplicar e dividir instruções.

A unidade de ponto flutuante é constituída por cinco unidades funcionais. Uma executa ponto flutuante acrescenta e subtrai, multiplica, divide e um quadrados de base. Duas unidades são para execução de instruções SIMD definidos pela Set Visual Instrução (VIS). O arquivo de registro de ponto flutuante contém trinta e dois registradores de 64 bits. Tem cinco portas de leitura e três portas de escrita.

esconderijo

O UltraSPARC tem dois níveis de cache, primário e secundário. Existem dois caches primárias, um para instruções e outro para dados. Ambos têm uma capacidade de 16 KB.

O UltraSPARC necessário um cache secundário externa obrigatória. O cache é unificado, tem uma capacidade de 512 KB e 4 MB e é direct-mapeada. Ele pode retornar dados em um único ciclo. A cache externo é implementado com SRAM síncronos cronometrado com a mesma frequência que o microprocessador, como rácios não foram apoiados. Ele é acessado através do barramento de dados.

Fabricação

Ele continha 3,8 milhões de transistores. Foi fabricado no processo de EPIC-3 da Texas Instruments, um 0,5 um complementar de metal-óxido-semicondutor processo (CMOS) com quatro níveis de metal. O UltraSPARC não foi fabricado em uma BiCMOS processo como Texas Instruments afirmou que não escala bem em 0,5 processos e ofereceu pouca melhora o desempenho. O processo foi aperfeiçoado na da TI MVP processador de sinal digital (DSP) com algumas características que faltam, tais como três níveis de metal em vez de quatro e um tamanho de 0,55 característica, antes de ser utilizado para fabricar o UltraSPARC para evitar a repetição dos problemas de fabricação encontrados com SuperSPARC .

Pacote

O UltraSPARC é embalado em um plástico 521-contacto ball grid array (PBGA).

processadores relacionados

Referências

- Greenley, D. et al. (1995). "UltraSPARC: A próxima geração superscalar 64-bit SPARC". Proceedings of Compcon '95 : pp. 442-451.

- Gwennap, Linley (3 Outubro 1994). "UltraSparc Lança SPARC Performance". Microprocessor Report , Volume 8, Number 13.

- Gwennap, Linley (5 Dezembro de 1994). "UltraSparc Adiciona instruções multimídia". Relatório microprocessador .