Multiprocessamento simétrico - Symmetric multiprocessing

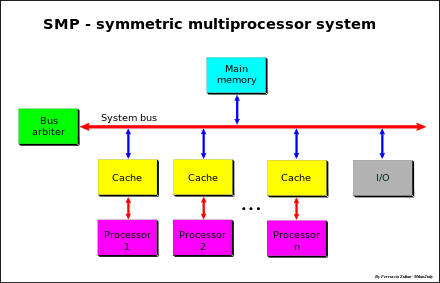

Multiprocessamento simétrico ou multiprocessamento de memória compartilhada ( SMP ) envolve um hardware de computador multiprocessador e arquitetura de software onde dois ou mais processadores idênticos são conectados a uma única memória principal compartilhada , têm acesso total a todos os dispositivos de entrada e saída e são controlados por um único instância do sistema operacional que trata todos os processadores igualmente, não reservando nenhum para finalidades especiais. A maioria dos sistemas multiprocessadores hoje usa uma arquitetura SMP. No caso de processadores com vários núcleos , a arquitetura SMP se aplica aos núcleos, tratando-os como processadores separados.

O professor John D. Kubiatowicz considera que os sistemas SMP tradicionalmente contêm processadores sem caches. Culler e Pal-Singh em seu livro de 1998 "Parallel Computer Architecture: A Hardware / Software Approach" mencionam: "O termo SMP é amplamente usado, mas causa um pouco de confusão. [...] A descrição mais precisa do que se pretende O SMP é um multiprocessador de memória compartilhada em que o custo de acesso a um local de memória é o mesmo para todos os processadores; ou seja, ele tem custos de acesso uniformes quando o acesso realmente é à memória. Se o local estiver em cache, o acesso será mais rápido, mas os tempos de acesso ao cache e os tempos de acesso à memória são iguais em todos os processadores. "

Sistemas SMP são multiprocessadores estreitamente acoplados sistemas com uma piscina de processadores homogéneos que funcionam de forma independente um do outro. Cada processador, executando diferentes programas e trabalhando em diferentes conjuntos de dados, tem a capacidade de compartilhar recursos comuns (memória, dispositivo de E / S, sistema de interrupção e assim por diante) que são conectados por meio de um barramento de sistema ou uma barra transversal .

Projeto

Os sistemas SMP têm memória compartilhada centralizada chamada memória principal (MM) operando em um único sistema operacional com dois ou mais processadores homogêneos. Normalmente, cada processador tem uma memória privada de alta velocidade associada, conhecida como memória cache (ou cache), para acelerar o acesso aos dados da memória principal e reduzir o tráfego do barramento do sistema.

Os processadores podem ser interconectados usando barramentos, switches crossbar ou redes mesh no chip. O gargalo na escalabilidade do SMP usando barramentos ou switches crossbar é a largura de banda e o consumo de energia da interconexão entre os vários processadores, a memória e as matrizes de disco. As arquiteturas de malha evitam esses gargalos e fornecem escalabilidade quase linear para contagens de processador muito mais altas, sacrificando a capacidade de programação:

Sérios desafios de programação permanecem com este tipo de arquitetura porque requer dois modos distintos de programação; uma para as próprias CPUs e outra para a interconexão entre as CPUs. Uma única linguagem de programação teria que ser capaz não apenas de particionar a carga de trabalho, mas também compreender a localidade da memória, o que é grave em uma arquitetura baseada em malha.

Os sistemas SMP permitem que qualquer processador trabalhe em qualquer tarefa, independentemente de onde os dados dessa tarefa estejam localizados na memória, desde que cada tarefa no sistema não esteja em execução em dois ou mais processadores ao mesmo tempo. Com o suporte adequado do sistema operacional , os sistemas SMP podem mover facilmente as tarefas entre os processadores para equilibrar a carga de trabalho com eficiência.

História

O primeiro sistema de produção com vários processadores idênticos foi o Burroughs B5000 , que funcionava por volta de 1961. No entanto, em tempo de execução isso era assimétrico , com um processador restrito a programas de aplicativos enquanto o outro processador lidava principalmente com o sistema operacional e interrupções de hardware. O Burroughs D825 implementou o SMP pela primeira vez em 1962.

A IBM ofereceu sistemas de computador de processador duplo baseados em seu System / 360 Modelo 65 e nos modelos 67 e 67–2 intimamente relacionados . Os sistemas operacionais que rodavam nessas máquinas eram OS / 360 M65MP e TSS / 360 . Outro software desenvolvido em universidades, notadamente o Michigan Terminal System (MTS), utilizou ambas as CPUs. Ambos os processadores podem acessar canais de dados e iniciar I / O. No OS / 360 M65MP, os periféricos geralmente podem ser conectados a qualquer um dos processadores, já que o kernel do sistema operacional é executado em ambos os processadores (embora com um "grande bloqueio" em torno do manipulador de E / S). O supervisor MTS (UMMPS) pode ser executado em ambas as CPUs do IBM System / 360 modelo 67–2. Os bloqueios do supervisor eram pequenos e usados para proteger estruturas de dados comuns individuais que podem ser acessadas simultaneamente de qualquer CPU.

Outros mainframes que suportavam SMP incluíam o UNIVAC 1108 II , lançado em 1965, que suportava até três CPUs, e o GE-635 e GE-645 , embora o GECOS em sistemas multiprocessador GE-635 funcionasse de forma assimétrica mestre-escravo, ao contrário de Multics em sistemas multiprocessadores GE-645, que funcionam de forma simétrica.

Começando com sua versão 7.0 (1972), o sistema operacional TOPS-10 da Digital Equipment Corporation implementou o recurso SMP, o sistema mais antigo executando SMP foi o sistema de processador dual KI10 DECSystem 1077 . O sistema KL10 posterior poderia agregar até 8 CPUs de maneira SMP. Em contraste, o primeiro sistema VAX multiprocessador da DEC , o VAX-11/782, era assimétrico, mas os sistemas multiprocessadores VAX posteriores eram SMP.

As primeiras implementações comerciais do Unix SMP incluíram o Sequent Computer Systems Balance 8000 (lançado em 1984) e o Balance 21000 (lançado em 1986). Ambos os modelos foram baseados em processadores National Semiconductor NS32032 de 10 MHz , cada um com um pequeno cache de gravação conectado a uma memória comum para formar um sistema de memória compartilhada . Outra implementação SMP Unix comercial inicial foi o Honeywell Information Systems Italy XPS-100 baseado em NUMA projetado por Dan Gielan da VAST Corporation em 1985. Seu design suportava até 14 processadores, mas devido a limitações elétricas, a maior versão comercializada era um sistema de processador duplo . O sistema operacional foi derivado e portado pela VAST Corporation do código AT&T 3B20 Unix SysVr3 usado internamente na AT&T.

Anteriormente existiam portas UNIX de multiprocessamento não comerciais, incluindo uma porta chamada MUNIX, criada na Naval Postgraduate School em 1975.

Usos

Os sistemas de servidor e compartilhamento de tempo geralmente podem usar SMP sem alterações nos aplicativos, pois eles podem ter vários processos em execução em paralelo, e um sistema com mais de um processo em execução pode executar processos diferentes em processadores diferentes.

Em computadores pessoais , o SMP é menos útil para aplicativos que não foram modificados. Se o sistema raramente executa mais de um processo por vez, o SMP é útil apenas para aplicativos que foram modificados para processamento multithread (multitarefa). O software com programação personalizada pode ser escrito ou modificado para usar vários threads, de modo que possa usar vários processadores.

Os programas multithread também podem ser usados em sistemas de compartilhamento de tempo e de servidor que oferecem suporte a multithreading, permitindo que façam mais uso de vários processadores.

Vantagens desvantagens

Nos sistemas SMP atuais, todos os processadores estão fortemente acoplados dentro da mesma caixa com um barramento ou switch; em sistemas SMP anteriores, uma única CPU ocupava um gabinete inteiro. Alguns dos componentes compartilhados são memória global, discos e dispositivos de E / S. Apenas uma cópia de um sistema operacional é executada em todos os processadores, e o sistema operacional deve ser projetado para tirar proveito dessa arquitetura. Algumas das vantagens básicas envolvem maneiras econômicas de aumentar o rendimento. Para resolver diferentes problemas e tarefas, o SMP aplica vários processadores a esse problema, conhecido como programação paralela .

No entanto, existem alguns limites na escalabilidade do SMP devido à coerência do cache e aos objetos compartilhados.

Programação

Os sistemas Uniprocessador e SMP requerem métodos de programação diferentes para atingir o desempenho máximo. Os programas em execução em sistemas SMP podem apresentar um aumento no desempenho, mesmo quando foram escritos para sistemas com um processador. Isso ocorre porque as interrupções de hardware geralmente suspendem a execução do programa, enquanto o kernel que as controla pode ser executado em um processador ocioso. O efeito na maioria dos aplicativos (por exemplo, jogos) não é tanto um aumento de desempenho, mas a aparência de que o programa está sendo executado com muito mais suavidade. Alguns aplicativos, particularmente software de construção e alguns projetos de computação distribuída , são executados mais rapidamente por um fator de (quase) o número de processadores adicionais. (Compiladores por si só são de thread único, mas, ao construir um projeto de software com várias unidades de compilação, se cada unidade de compilação for tratada de forma independente, isso cria uma situação embaraçosamente paralela em todo o projeto de unidade de multi-compilação, permitindo um escalonamento quase linear da compilação tempo. Os projetos de computação distribuída são inerentemente paralelos por design.)

Os programadores de sistemas devem construir suporte para SMP no sistema operacional , caso contrário, os processadores adicionais permanecem ociosos e o sistema funciona como um sistema de um processador.

Os sistemas SMP também podem levar a mais complexidade em relação aos conjuntos de instruções. Um sistema de processador homogêneo normalmente requer registros extras para "instruções especiais", como SIMD (MMX, SSE, etc.), enquanto um sistema heterogêneo pode implementar diferentes tipos de hardware para diferentes instruções / usos.

atuação

Quando mais de um programa é executado ao mesmo tempo, um sistema SMP tem um desempenho consideravelmente melhor do que um uni-processador, porque diferentes programas podem ser executados em diferentes CPUs simultaneamente. Por outro lado, o multiprocessamento assimétrico (AMP) geralmente permite que apenas um processador execute um programa ou tarefa por vez. Por exemplo, o AMP pode ser usado para atribuir tarefas específicas à CPU com base na prioridade e na importância da conclusão da tarefa. O AMP foi criado bem antes do SMP em termos de manipulação de várias CPUs, o que explica a falta de desempenho com base no exemplo fornecido.

Nos casos em que um ambiente SMP processa muitos trabalhos, os administradores geralmente experimentam uma perda de eficiência do hardware. Programas de software foram desenvolvidos para agendar trabalhos e outras funções do computador para que a utilização do processador atinja seu potencial máximo. Bons pacotes de software podem atingir esse potencial máximo agendando cada CPU separadamente, bem como sendo capazes de integrar várias máquinas SMP e clusters.

O acesso à RAM é serializado; isso e os problemas de coerência do cache fazem com que o desempenho fique um pouco atrás do número de processadores adicionais no sistema.

Alternativas

O SMP usa um único barramento de sistema compartilhado que representa um dos primeiros estilos de arquiteturas de máquina com multiprocessador, normalmente usado para construir computadores menores com até 8 processadores.

Sistemas de computador maiores podem usar arquiteturas mais recentes, como NUMA (Non-Uniform Memory Access), que dedica diferentes bancos de memória a diferentes processadores. Em uma arquitetura NUMA, os processadores podem acessar a memória local rapidamente e a memória remota mais lentamente. Isso pode melhorar drasticamente o rendimento da memória, desde que os dados sejam localizados em processos específicos (e, portanto, processadores). Por outro lado, o NUMA torna o custo de mover dados de um processador para outro, como no balanceamento de carga de trabalho, mais caro. Os benefícios do NUMA são limitados a cargas de trabalho específicas, principalmente em servidores onde os dados costumam estar fortemente associados a certas tarefas ou usuários.

Finalmente, existe o multiprocessamento em cluster de computador (como Beowulf ), no qual nem toda a memória está disponível para todos os processadores. As técnicas de agrupamento são usadas de forma bastante extensa para construir supercomputadores muito grandes.

Variável SMP

O Multiprocessamento Simétrico Variável (vSMP) é uma tecnologia de caso de uso móvel específica iniciada pela NVIDIA. Essa tecnologia inclui um quinto núcleo extra em um dispositivo quad-core, chamado de núcleo Companion, construído especificamente para executar tarefas em uma frequência mais baixa durante o modo de espera ativo móvel, reprodução de vídeo e reprodução de música.

O Projeto Kal-El ( Tegra 3 ), patenteado pela NVIDIA, foi o primeiro SoC (System on Chip) a implementar essa nova tecnologia vSMP. Essa tecnologia não apenas reduz o consumo de energia móvel durante o estado de espera ativa, mas também maximiza o desempenho do quad core durante o uso ativo para aplicativos móveis intensivos. No geral, essa tecnologia atende à necessidade de aumentar o desempenho da vida útil da bateria durante o uso ativo e em espera, reduzindo o consumo de energia em processadores móveis.

Ao contrário das arquiteturas SMP atuais, o núcleo vSMP Companion é transparente para o SO, o que significa que o sistema operacional e os aplicativos em execução desconhecem totalmente esse núcleo extra, mas ainda podem aproveitá-lo. Algumas das vantagens da arquitetura vSMP incluem coerência de cache, eficiência do sistema operacional e otimização de energia. As vantagens desta arquitetura são explicadas a seguir:

- Coerência de cache: não há consequências para sincronizar caches entre núcleos rodando em frequências diferentes, uma vez que o vSMP não permite que o núcleo Companion e os núcleos principais sejam executados simultaneamente.

- Eficiência do sistema operacional: é ineficiente quando vários núcleos da CPU são executados em diferentes frequências assíncronas porque isso pode levar a possíveis problemas de agendamento. Com o vSMP, os núcleos da CPU ativos serão executados em frequências semelhantes para otimizar o agendamento do sistema operacional.

- Otimização de energia: Na arquitetura baseada em clocking assíncrono, cada núcleo está em um plano de energia diferente para lidar com ajustes de tensão para diferentes frequências de operação. O resultado disso pode afetar o desempenho. A tecnologia vSMP é capaz de ativar e desativar dinamicamente certos núcleos para uso ativo e em espera, reduzindo o consumo geral de energia.

Essas vantagens levam a arquitetura vSMP a se beneficiar consideravelmente em relação a outras arquiteturas que usam tecnologias de relógio assíncrono.

Veja também

- Multiprocessamento assimétrico

- Máquina Binary Modular Dataflow

- Local (hardware de computador)

- Maciçamente paralelo

- Espaço de endereço global particionado

- Multithreading simultâneo - onde os elementos funcionais de um núcleo da CPU são alocados em vários threads de execução

- Bloqueio de software

- Xeon Phi