Loop de fase - Phase-locked loop

Um loop de bloqueio de fase ou loop de bloqueio de fase ( PLL ) é um sistema de controle que gera um sinal de saída cuja fase está relacionada à fase de um sinal de entrada. Existem vários tipos diferentes; o mais simples é um circuito eletrônico que consiste em um oscilador de frequência variável e um detector de fase em um loop de feedback . O oscilador gera um sinal periódico, e o detector de fase compara a fase desse sinal com a fase do sinal periódico de entrada, ajustando o oscilador para manter as fases casadas.

Manter a fase de entrada e saída em passo de bloqueio também implica em manter as mesmas frequências de entrada e saída. Consequentemente, além de sincronizar os sinais, um loop de bloqueio de fase pode rastrear uma frequência de entrada ou pode gerar uma frequência que é um múltiplo da frequência de entrada. Essas propriedades são usadas para sincronização do relógio do computador, demodulação e síntese de frequência .

Os loops com bloqueio de fase são amplamente empregados em rádio , telecomunicações , computadores e outras aplicações eletrônicas. Eles podem ser usados para demodular um sinal, recuperar um sinal de um canal de comunicação ruidoso, gerar uma frequência estável em múltiplos de uma frequência de entrada ( síntese de frequência ) ou distribuir pulsos de relógio precisamente cronometrados em circuitos lógicos digitais, como microprocessadores . Uma vez que um único circuito integrado pode fornecer um bloco de construção de loop bloqueado de fase completo, a técnica é amplamente usada em dispositivos eletrônicos modernos, com frequências de saída de uma fração de hertz até muitos gigahertz.

Analogias práticas

Analogia da corrida de automóveis

Como uma analogia de um PLL, considere uma corrida entre dois carros. Um representa a frequência de entrada, o outro a frequência do oscilador controlado por tensão de saída (VCO) do PLL . Cada volta corresponde a um ciclo completo. O número de voltas por hora (uma velocidade) corresponde à frequência. A separação dos carros (uma distância) corresponde à diferença de fase entre os dois sinais oscilantes.

Durante a maior parte da corrida, cada carro está sozinho e livre para ultrapassar o outro e dar voltas no outro. Isso é análogo ao PLL em um estado desbloqueado.

No entanto, se houver um acidente, uma bandeira amarela de advertência é levantada. Isso significa que nenhum dos carros de corrida tem permissão para ultrapassar e ultrapassar o outro carro. Os dois carros de corrida representam a frequência de entrada e saída do PLL em um estado travado. Cada piloto medirá a diferença de fase (uma fração da distância ao redor da volta) entre eles e o outro carro de corrida. Se o condutor traseiro estiver muito longe, eles aumentarão a velocidade para fechar a lacuna. Se eles estiverem muito próximos do outro carro, o motorista irá reduzir a velocidade. O resultado é que os dois carros de corrida circularão a pista em sincronia com uma diferença de fase fixa (ou distância constante) entre eles. Como nenhum carro pode dar voltas no outro, os carros fazem o mesmo número de voltas em um determinado período de tempo. Portanto, a frequência dos dois sinais é a mesma.

Analogia do relógio

A fase pode ser proporcional ao tempo, portanto, uma diferença de fase pode ser uma diferença de tempo. Os relógios são, com vários graus de precisão, travados por fase (travados por tempo) para um relógio líder.

Deixado sozinho, cada relógio marcará o tempo em taxas ligeiramente diferentes. Um relógio de parede, por exemplo, pode ser rápido alguns segundos por hora em comparação com o relógio de referência no NIST . Com o tempo, essa diferença de tempo se tornaria substancial.

Para manter o relógio de parede sincronizado com o relógio de referência, a cada semana o proprietário compara a hora em seu relógio de parede com um relógio mais preciso (uma comparação de fase) e zera o relógio. Deixado sozinho, o relógio de parede continuará a divergir do relógio de referência na mesma taxa de alguns segundos por hora.

Alguns relógios têm um ajuste de tempo (um controle rápido-lento). Quando o proprietário comparou a hora do relógio de parede com a hora de referência, percebeu que o relógio estava muito rápido. Conseqüentemente, o proprietário poderia ajustar o tempo um pouco para fazer o relógio funcionar um pouco mais lento (frequência). Se as coisas funcionarem bem, o relógio será mais preciso do que antes. Após uma série de ajustes semanais, a noção de segundo do relógio de parede concordaria com o tempo de referência (bloqueado tanto em frequência quanto em fase na estabilidade do relógio de parede).

Uma versão eletromecânica inicial de um loop de bloqueio de fase foi usada em 1921 no relógio Shortt-Synchronome .

História

A sincronização espontânea de relógios de pêndulo fracamente acoplados foi observada pelo físico holandês Christiaan Huygens já em 1673. Por volta da virada do século 19, Lord Rayleigh observou a sincronização de tubos de órgão fracamente acoplados e diapasões. Em 1919, WH Eccles e JH Vincent descobriram que dois osciladores eletrônicos que tinham sido ajustados para oscilar em frequências ligeiramente diferentes, mas que estavam acoplados a um circuito ressonante, logo oscilariam na mesma frequência. A sincronização automática de osciladores eletrônicos foi descrita em 1923 por Edward Victor Appleton .

Em 1925, o professor David Robertson, primeiro professor de engenharia elétrica da Universidade de Bristol , introduziu o bloqueio de fase em seu design de relógio para controlar o toque do sino Great George no novo Wills Memorial Building. O relógio de Robertson incorporava um dispositivo eletromecânico que podia variar a taxa de oscilação do pêndulo e derivava sinais de correção de um circuito que comparava a fase do pêndulo com a de um pulso telegráfico de entrada do Observatório de Greenwich todas as manhãs às 10h GMT. Além de incluir equivalentes de cada elemento de um PLL eletrônico moderno, o sistema de Robertson era notável pelo fato de seu detector de fase ser uma implementação lógica de relé do detector de fase / frequência não visto em circuitos eletrônicos até os anos 1970. O trabalho de Robertson antecedeu a pesquisa para o que mais tarde foi nomeado o loop-bloqueio de fase em 1932, quando pesquisadores britânicos desenvolveu uma alternativa para Edwin Armstrong 's receptor superheterodyne , o homódinas ou receptor de conversão direta . No sistema homódino ou sincródino, um oscilador local era sintonizado na frequência de entrada desejada e multiplicado pelo sinal de entrada. O sinal de saída resultante incluía as informações de modulação originais. A intenção era desenvolver um circuito receptor alternativo que exigisse menos circuitos sintonizados do que o receptor super-heteródino. Como o oscilador local mudaria rapidamente de frequência, um sinal de correção automática foi aplicado ao oscilador, mantendo-o na mesma fase e frequência do sinal desejado. A técnica foi descrita em 1932, em artigo de Henri de Bellescize, no jornal francês L'Onde Électrique .

Em receptores de televisão analógica, pelo menos desde o final dos anos 1930, os circuitos de varredura horizontal e vertical de loop de fase bloqueada são bloqueados para pulsos de sincronização no sinal de transmissão.

Quando a Signetics introduziu uma linha de circuitos integrados monolíticos como o NE565, que eram sistemas completos de loop de fase bloqueada em um chip em 1969, as aplicações da técnica se multiplicaram. Alguns anos depois, a RCA introduziu o circuito integrado " CD4046 " CMOS Micropower Phase-Locked, que se tornou um circuito integrado popular.

Estrutura e função

Os mecanismos de loop de bloqueio de fase podem ser implementados como circuitos analógicos ou digitais. Ambas as implementações usam a mesma estrutura básica. Os circuitos PLL analógicos incluem quatro elementos básicos:

- Detector de fase ,

- Filtro passa-baixa ,

- Oscilador controlado por tensão , e

- caminho de feedback (que pode incluir um divisor de frequência ).

Variações

Existem várias variações de PLLs. Alguns termos usados são loop analógico de bloqueio de fase (APLL), também conhecido como loop de bloqueio de fase linear (LPLL), loop de bloqueio de fase digital (DPLL), loop de bloqueio de fase digital (ADPLL) e fase de software loop bloqueado (SPLL).

- PLL analógico ou linear (APLL)

- O detector de fase é um multiplicador analógico. O filtro de loop está ativo ou passivo. Usa um oscilador controlado por tensão (VCO). APLL é considerado um tipo II se seu filtro de loop tem função de transferência com exatamente um pólo na origem (veja também a conjectura de Egan sobre a faixa pull-in do APLL tipo II ).

- PLL digital (DPLL)

- Um PLL analógico com um detector de fase digital (como XOR, trigger de borda JK, detector de frequência de fase). Pode ter divisor digital no loop.

- PLL totalmente digital (ADPLL)

- O detector de fase, filtro e oscilador são digitais. Usa um oscilador controlado numericamente (NCO).

- PLL de software (SPLL)

- Os blocos funcionais são implementados por software em vez de hardware especializado.

- PLL da bomba de carga (CP-PLL)

- CP-PLL é uma modificação de loops de bloqueio de fase com detector de frequência de fase e sinais de forma de onda quadrada. Veja também a conjectura de Gardner sobre CP-PLL .

Parâmetros de desempenho

- Digite e peça.

- Faixas de frequência : faixa de retenção (faixa de rastreamento), faixa de pull-in (faixa de captura, faixa de aquisição), faixa de bloqueio. Veja também o problema de Gardner no intervalo de bloqueio , a conjectura de Egan sobre o intervalo de puxão do APLL tipo II .

- Largura de banda do loop: Definindo a velocidade do loop de controle.

- Resposta transitória: como ultrapassagem e tempo de acomodação com uma certa precisão (como 50 ppm).

- Erros de estado estacionário: como fase restante ou erro de tempo.

- Pureza do espectro de saída: Como bandas laterais geradas a partir de uma certa ondulação de tensão de sintonia VCO.

- Ruído de fase: Definido pela energia do ruído em uma certa banda de frequência (como deslocamento de 10 kHz da portadora). Altamente dependente do ruído de fase VCO, largura de banda PLL, etc.

- Parâmetros gerais: como consumo de energia, faixa de tensão de alimentação, amplitude de saída, etc.

Formulários

Os loops com bloqueio de fase são amplamente usados para fins de sincronização ; em comunicações espaciais para demodulação coerente e extensão de limite , sincronização de bits e sincronização de símbolos. Loops com bloqueio de fase também podem ser usados para demodular sinais modulados por frequência . Em transmissores de rádio, um PLL é usado para sintetizar novas frequências que são um múltiplo de uma frequência de referência, com a mesma estabilidade da frequência de referência.

Outros aplicativos incluem

- Demodulação da modulação de frequência (FM): Se o PLL estiver bloqueado para um sinal FM, o VCO rastreia a frequência instantânea do sinal de entrada. A tensão de erro filtrada que controla o VCO e mantém o bloqueio com o sinal de entrada é a saída FM demodulada. As características de transferência do VCO determinam a linearidade da saída demodulada. Como o VCO usado em um PLL de circuito integrado é altamente linear, é possível realizar demoduladores FM altamente lineares.

- Demodulação de chaveamento por deslocamento de frequência (FSK): Na comunicação digital de dados e periféricos de computador, os dados binários são transmitidos por meio de uma frequência portadora que é deslocada entre duas frequências predefinidas.

- Recuperação de pequenos sinais que de outra forma seriam perdidos no ruído ( amplificador lock-in para rastrear a frequência de referência)

- Recuperação de informações de tempo de relógio de um fluxo de dados, como de uma unidade de disco

- Multiplicadores de clock em microprocessadores que permitem que os elementos do processador interno funcionem mais rápido do que as conexões externas, mantendo relações de temporização precisas

- Demodulação de modems e outros sinais de tom para telecomunicações e controle remoto .

- DSP de sinais de vídeo ; Os loops de bloqueio de fase também são usados para sincronizar a fase e a frequência com o sinal de vídeo analógico de entrada para que possa ser amostrado e processado digitalmente

- Microscopia de força atômica no modo de modulação de frequência , para detectar mudanças na frequência de ressonância do cantilever devido às interações da superfície da ponta

- Acionamento do motor DC

Recuperação de relógio

Alguns fluxos de dados, especialmente os fluxos de dados seriais de alta velocidade (como o fluxo bruto de dados da cabeça magnética de uma unidade de disco), são enviados sem um relógio de acompanhamento. O receptor gera um relógio a partir de uma referência de frequência aproximada e, em seguida, alinha a fase às transições no fluxo de dados com um PLL. Esse processo é conhecido como recuperação do relógio . Para que esse esquema funcione, o fluxo de dados deve ter uma transição com frequência suficiente para corrigir qualquer desvio no oscilador do PLL. Normalmente, algum tipo de código de linha , como codificação 8b / 10b , é usado para colocar um limite superior rígido no tempo máximo entre as transições.

Deskewing

Se um relógio for enviado em paralelo com os dados, esse relógio pode ser usado para amostrar os dados. Como o relógio deve ser recebido e amplificado antes de acionar os flip-flops que amostram os dados, haverá um atraso finito e dependente do processo, da temperatura e da tensão entre a transição do relógio detectada e a janela de dados recebida. Esse atraso limita a frequência com que os dados podem ser enviados. Uma maneira de eliminar esse atraso é incluir um PLL de enquadramento no lado do recebimento, de modo que o relógio em cada flip-flop de dados seja compatível com a fase do relógio recebido. Nesse tipo de aplicativo, uma forma especial de um PLL chamada loop bloqueado por atraso (DLL) é freqüentemente usada.

Geração de relógio

Muitos sistemas eletrônicos incluem processadores de vários tipos que operam a centenas de megahertz. Normalmente, os clocks fornecidos a esses processadores vêm de PLLs geradores de clock, que multiplicam um clock de referência de frequência inferior (geralmente 50 ou 100 MHz) até a frequência de operação do processador. O fator de multiplicação pode ser muito grande nos casos em que a frequência operacional é de vários gigahertz e o cristal de referência é apenas dezenas ou centenas de megahertz.

Espalhe o espectro

Todos os sistemas eletrônicos emitem alguma energia de radiofrequência indesejada. Várias agências reguladoras (como a FCC nos Estados Unidos) colocam limites na energia emitida e qualquer interferência causada por ela. O ruído emitido geralmente aparece em picos espectrais agudos (geralmente na frequência de operação do dispositivo e alguns harmônicos). Um projetista de sistema pode usar um PLL de espalhamento espectral para reduzir a interferência com receptores de alto Q, espalhando a energia por uma porção maior do espectro. Por exemplo, alterando a frequência operacional para cima e para baixo em uma pequena quantidade (cerca de 1%), um dispositivo rodando em centenas de megahertz pode espalhar sua interferência uniformemente em alguns megahertz de espectro, o que reduz drasticamente a quantidade de ruído visto na transmissão Canais de rádio FM , que têm largura de banda de várias dezenas de quilohertz.

Distribuição de relógio

Normalmente, o clock de referência entra no chip e aciona um loop de travamento de fase ( PLL ), que aciona a distribuição do clock do sistema. A distribuição do relógio é geralmente balanceada de modo que o relógio chegue a todos os terminais simultaneamente. Um desses pontos finais é a entrada de feedback do PLL. A função do PLL é comparar o relógio distribuído com o relógio de referência de entrada e variar a fase e a frequência de sua saída até que os relógios de referência e de realimentação tenham uma correspondência de fase e frequência.

Os PLLs são onipresentes - eles ajustam relógios em sistemas com vários metros de largura, bem como relógios em pequenas porções de chips individuais. Às vezes, o relógio de referência pode não ser realmente um relógio puro, mas sim um fluxo de dados com transições suficientes para que o PLL seja capaz de recuperar um relógio regular desse fluxo. Às vezes, o relógio de referência tem a mesma frequência do relógio acionado pela distribuição do relógio, outras vezes, o relógio distribuído pode ser algum múltiplo racional da referência.

Detecção AM

Um PLL pode ser usado para demodular sincronicamente sinais modulados em amplitude (AM). O PLL recupera a fase e a frequência da portadora do sinal AM de entrada. A fase recuperada no VCO difere da portadora em 90 °, então ela é deslocada em fase para corresponder e, em seguida, alimentada para um multiplicador. A saída do multiplicador contém os sinais de soma e diferença de frequência, e a saída demodulada é obtida por filtragem de passagem baixa. Uma vez que o PLL responde apenas às frequências portadoras que estão muito próximas da saída do VCO, um detector PLL AM exibe um alto grau de seletividade e imunidade a ruído que não é possível com demoduladores AM convencionais de tipo de pico. No entanto, o loop pode perder o bloqueio onde os sinais AM têm profundidade de modulação de 100%.

Redução de instabilidade e ruído

Uma propriedade desejável de todos os PLLs é que as bordas do clock de referência e feedback sejam colocadas em um alinhamento muito próximo. A diferença média de tempo entre as fases dos dois sinais quando o PLL atingiu o bloqueio é chamada de deslocamento de fase estática (também chamado de erro de fase em estado estacionário ). A variação entre essas fases é chamada de jitter de rastreamento . Idealmente, o deslocamento de fase estática deve ser zero e o jitter de rastreamento deve ser o mais baixo possível.

O ruído de fase é outro tipo de jitter observado em PLLs e é causado pelo próprio oscilador e por elementos usados no circuito de controle de frequência do oscilador. Algumas tecnologias são conhecidas por apresentarem melhor desempenho do que outras nesse aspecto. Os melhores PLLs digitais são construídos com elementos lógicos acoplados ao emissor ( ECL ), em detrimento do alto consumo de energia. Para manter o ruído de fase baixo nos circuitos PLL, é melhor evitar a saturação de famílias lógicas, como a lógica transistor-transistor ( TTL ) ou CMOS .

Outra propriedade desejável de todos os PLLs é que a fase e a frequência do relógio gerado não sejam afetadas por mudanças rápidas nas tensões das linhas de alimentação de energia e aterramento, bem como a tensão do substrato no qual os circuitos PLL são fabricados. Isso é chamado de rejeição de substrato e ruído de alimentação . Quanto maior a rejeição de ruído, melhor.

Para melhorar ainda mais o ruído de fase da saída, um oscilador travado por injeção pode ser empregado seguindo o VCO no PLL.

Síntese de freqüência

Em sistemas de comunicação digital sem fio (GSM, CDMA etc.), os PLLs são usados para fornecer conversão ascendente do oscilador local durante a transmissão e conversão descendente durante a recepção. Na maioria dos aparelhos celulares, essa função foi amplamente integrada em um único circuito integrado para reduzir o custo e o tamanho do aparelho. No entanto, devido ao alto desempenho exigido dos terminais da estação base, os circuitos de transmissão e recepção são construídos com componentes discretos para atingir os níveis de desempenho exigidos. Os módulos do oscilador local GSM são normalmente construídos com um circuito integrado de sintetizador de frequência e VCOs de ressonador discreto.

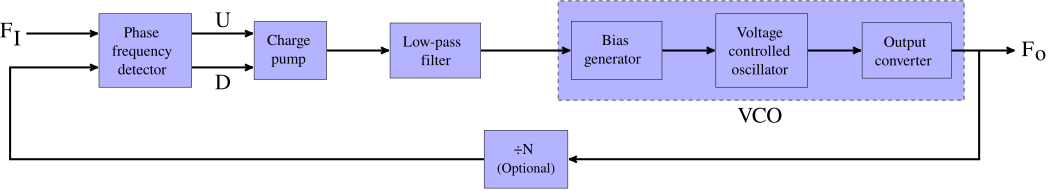

Diagrama de bloco

Um detector de fase compara dois sinais de entrada e produz um sinal de erro que é proporcional à diferença de fase. O sinal de erro é filtrado e usado para acionar um VCO que cria uma fase de saída. A saída é alimentada por meio de um divisor opcional de volta à entrada do sistema, produzindo um loop de feedback negativo . Se a fase de saída se desviar, o sinal de erro aumentará, conduzindo a fase de VCO na direção oposta para reduzir o erro. Assim, a fase de saída é bloqueada para a fase na outra entrada. Essa entrada é chamada de referência.

Os loops de bloqueio de fase analógico geralmente são construídos com um detector de fase analógico, filtro passa-baixo e VCO colocados em uma configuração de feedback negativo . Um loop de bloqueio de fase digital usa um detector de fase digital; ele também pode ter um divisor no caminho de feedback ou no caminho de referência, ou ambos, a fim de tornar a frequência do sinal de saída do PLL um múltiplo racional da frequência de referência. Um múltiplo não inteiro da frequência de referência também pode ser criado substituindo o contador simples de divisão por N no caminho de feedback por um contador de deglutição de pulso programável . Esta técnica é geralmente referida como um sintetizador N-fracionário ou PLL N-fracionário.

O oscilador gera um sinal de saída periódico. Suponha que inicialmente o oscilador esteja quase na mesma frequência que o sinal de referência. Se a fase do oscilador ficar para trás daquela da referência, o detector de fase muda a tensão de controle do oscilador para que ele acelere. Da mesma forma, se a fase avançar lentamente em relação à referência, o detector de fase altera a tensão de controle para desacelerar o oscilador. Uma vez que inicialmente o oscilador pode estar longe da frequência de referência, os detectores de fase práticos também podem responder às diferenças de frequência, de modo a aumentar a faixa de bloqueio de entradas permitidas. Dependendo da aplicação, a saída do oscilador controlado ou o sinal de controle para o oscilador fornecem a saída útil do sistema PLL.

Elementos

Detector de fase

Um detector de fase (PD) gera uma tensão, que representa a diferença de fase entre dois sinais. Em um PLL, as duas entradas do detector de fase são a entrada de referência e o feedback do VCO. A tensão de saída PD é usada para controlar o VCO de forma que a diferença de fase entre as duas entradas seja mantida constante, tornando-o um sistema de feedback negativo.

Diferentes tipos de detectores de fase têm diferentes características de desempenho.

Por exemplo, o misturador de frequência produz harmônicos que adicionam complexidade em aplicações onde a pureza espectral do sinal VCO é importante. As bandas laterais indesejadas (espúrias) resultantes, também chamadas de " esporas de referência ", podem dominar os requisitos do filtro e reduzir o intervalo de captura bem abaixo ou aumentar o tempo de bloqueio além dos requisitos. Nessas aplicações, os detectores de fase digital mais complexos são usados, os quais não têm um componente de spur de referência tão severo em sua saída. Além disso, quando travado, a diferença de fase em estado estacionário nas entradas que usam esse tipo de detector de fase é de quase 90 graus.

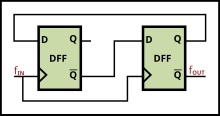

Em aplicações PLL, é freqüentemente necessário saber quando o loop está fora de bloqueio. Os detectores de frequência de fase digital mais complexos geralmente têm uma saída que permite uma indicação confiável de uma condição fora de bloqueio.

Uma porta XOR é freqüentemente usada para PLLs digitais como um detector de fase simples, porém eficaz. Ele também pode ser usado em um sentido analógico com apenas uma ligeira modificação no circuito.

Filtro

O bloco comumente chamado de filtro de loop PLL (geralmente um filtro passa-baixo) geralmente tem duas funções distintas.

A função principal é determinar a dinâmica do loop, também chamada de estabilidade . É assim que o loop responde a distúrbios, como mudanças na frequência de referência, mudanças no divisor de feedback ou na inicialização. As considerações comuns são a faixa sobre a qual o loop pode atingir o bloqueio (faixa de pull-in, faixa de bloqueio ou faixa de captura), a rapidez com que o loop atinge o bloqueio (tempo de bloqueio, tempo de bloqueio ou tempo de acomodação ) e comportamento de amortecimento . Dependendo da aplicação, isso pode exigir um ou mais dos seguintes: uma proporção simples (ganho ou atenuação), uma integral (filtro passa-baixa) e / ou derivada ( filtro passa-alta ). Os parâmetros de loop comumente examinados para isso são a margem de ganho e a margem de fase do loop . Conceitos comuns na teoria de controle, incluindo o controlador PID, são usados para projetar esta função.

A segunda consideração comum é limitar a quantidade de energia de frequência de referência (ondulação) que aparece na saída do detector de fase que é então aplicada à entrada de controle VCO. Esta frequência modula o VCO e produz bandas laterais FM comumente chamadas de "spurs de referência".

O design desse bloco pode ser dominado por qualquer uma dessas considerações ou pode ser um processo complexo que concilia as interações dos dois. As compensações típicas são o aumento da largura de banda, geralmente degrada a estabilidade ou muito amortecimento para uma melhor estabilidade reduzirá a velocidade e aumentará o tempo de estabilização. Freqüentemente, também o ruído de fase é afetado.

Oscilador

Todos os loops com bloqueio de fase empregam um elemento oscilador com capacidade de frequência variável. Este pode ser um VCO analógico acionado por circuitos analógicos no caso de um APLL ou acionado digitalmente por meio do uso de um conversor digital para analógico, como é o caso de alguns projetos DPLL. Os osciladores digitais puros, como um oscilador controlado numericamente, são usados em ADPLLs.

Caminho de feedback e divisor opcional

PLLs podem incluir um divisor entre o oscilador e a entrada de feedback para o detector de fase para produzir um sintetizador de frequência . Um divisor programável é particularmente útil em aplicações de transmissor de rádio, uma vez que um grande número de frequências de transmissão pode ser produzido a partir de um único oscilador de referência controlado por cristal de quartzo estável, preciso, mas caro .

Alguns PLLs também incluem um divisor entre o relógio de referência e a entrada de referência para o detector de fase. Se o divisor no caminho de feedback for dividido por e o divisor de entrada de referência por , ele permite que o PLL multiplique a frequência de referência por . Pode parecer mais simples apenas alimentar o PLL com uma frequência mais baixa, mas em alguns casos a frequência de referência pode ser restringida por outros problemas e, então, o divisor de referência é útil.

A multiplicação da frequência também pode ser obtida travando a saída do VCO no N- ésimo harmônico do sinal de referência. Em vez de um detector de fase simples, o projeto usa um misturador harmônico (misturador de amostragem). O misturador harmônico transforma o sinal de referência em um trem de impulso rico em harmônicos. A saída do VCO é sintonizada grosseiramente para ficar perto de um desses harmônicos. Consequentemente, a saída do misturador harmônico desejada (representando a diferença entre o harmônico N e a saída VCO) cai dentro da banda passante do filtro de loop.

Também deve ser observado que o feedback não se limita a um divisor de frequência. Este elemento pode ser outros elementos, como um multiplicador de frequência ou um mixer. O multiplicador tornará a saída do VCO um sub-múltiplo (ao invés de um múltiplo) da frequência de referência. Um mixer pode traduzir a frequência VCO por um deslocamento fixo. Também pode ser uma combinação dos dois. Um exemplo é um divisor seguindo um mixer; isso permite que o divisor opere em uma frequência muito mais baixa do que o VCO sem perda de ganho de loop.

Modelagem

Modelo de domínio do tempo de APLL

As equações que governam um circuito fechado de fase com um multiplicador analógico como o detector de fase e o filtro linear podem ser derivadas da seguinte forma. Deixe que a entrada para o detector de fase seja e a saída do VCO seja com fases e . As funções e descrevem formas de onda de sinais. Então, a saída do detector de fase é dada por

A frequência VCO é geralmente tomada como uma função da entrada VCO como

onde é a sensibilidade do VCO e é expressa em Hz / V; é uma frequência de funcionamento livre de VCO.

O filtro de loop pode ser descrito por um sistema de equações diferenciais lineares

onde é uma entrada do filtro, é uma saída do filtro, é -por- matriz ,. representa um estado inicial do filtro. O símbolo da estrela é uma transposta conjugada .

Portanto, o sistema a seguir descreve PLL

onde é uma mudança de fase inicial.

Modelo de domínio de fase de APLL

Considere que a entrada do PLL e a saída do VCO são sinais de alta frequência. Então, para quaisquer funções diferenciáveis por partes -periódicas e há uma função tal que a saída de Filter

no domínio da fase é assintoticamente igual (a diferença é pequena em relação às frequências) à saída do filtro no modelo no domínio do tempo. Aqui, a função é uma característica do detector de fase .

Denote pela diferença de fase

Em seguida, o seguinte sistema dinâmico descreve o comportamento PLL

Aqui ; é a frequência de um oscilador de referência (presumimos que seja constante).

Exemplo

Considere sinais sinusoidais

e um circuito RC monopolar simples como filtro. O modelo de domínio do tempo assume a forma

As características de PD para estes sinais são iguais a

Portanto, o modelo de domínio de fase assume a forma

Este sistema de equações é equivalente à equação do pêndulo matemático

Modelo de domínio de fase linearizado

Os loops de bloqueio de fase também podem ser analisados como sistemas de controle aplicando a transformada de Laplace . A resposta do loop pode ser escrita como

Onde

- é a fase de saída em radianos

- é a fase de entrada em radianos

- é o ganho do detector de fase em volts por radiano

- é o ganho de VCO em radianos por volt- segundo

- é a função de transferência do filtro de loop (adimensional)

As características do loop podem ser controladas inserindo diferentes tipos de filtros de loop. O filtro mais simples é um circuito RC monopolar . A função de transferência de loop, neste caso, é

A resposta do loop torna-se:

Esta é a forma de um oscilador harmônico clássico . O denominador pode estar relacionado ao de um sistema de segunda ordem:

onde é o fator de amortecimento e é a frequência natural do loop.

Para o filtro RC monopolar,

A frequência natural do loop é uma medida do tempo de resposta do loop e o fator de amortecimento é uma medida do overshoot e toque. Idealmente, a frequência natural deve ser alta e o fator de amortecimento deve ser próximo a 0,707 (amortecimento crítico). Com um filtro de pólo único, não é possível controlar a frequência do loop e o fator de amortecimento de forma independente. Para o caso de amortecimento crítico,

Um filtro um pouco mais eficaz, o filtro lag-lead inclui um pólo e um zero. Isso pode ser realizado com dois resistores e um capacitor. A função de transferência para este filtro é

Este filtro tem duas constantes de tempo

Substituir acima resulta na seguinte frequência natural e fator de amortecimento

Os componentes do filtro de loop podem ser calculados independentemente para uma determinada frequência natural e fator de amortecimento

O design do filtro de loop do mundo real pode ser muito mais complexo, por exemplo, usando filtros de ordem superior para reduzir vários tipos ou fontes de ruído de fase. (Veja o D Banerjee ref abaixo)

Implementar um loop digital de bloqueio de fase no software

Loops de fase digital podem ser implementados em hardware, usando circuitos integrados como um CMOS 4046. No entanto, com os microcontroladores se tornando mais rápidos, pode fazer sentido implementar um loop de fase bloqueada em software para aplicações que não requerem travamento em sinais em MHz alcance ou mais rápido, como controlar com precisão as velocidades do motor. A implementação do software tem várias vantagens, incluindo fácil customização do loop de feedback, incluindo a alteração da razão de multiplicação ou divisão entre o sinal sendo rastreado e o oscilador de saída. Além disso, uma implementação de software é útil para entender e experimentar. Como um exemplo de um loop de bloqueio de fase implementado usando um detector de frequência de fase é apresentado no MATLAB, já que este tipo de detector de fase é robusto e fácil de implementar.

% This example is written in MATLAB

% Initialize variables

vcofreq = zeros(1, numiterations);

ervec = zeros(1, numiterations);

% Keep track of last states of reference, signal, and error signal

qsig = 0; qref = 0; lref = 0; lsig = 0; lersig = 0;

phs = 0;

freq = 0;

% Loop filter constants (proportional and derivative)

% Currently powers of two to facilitate multiplication by shifts

prop = 1 / 128;

deriv = 64;

for it = 1:numiterations

% Simulate a local oscillator using a 16-bit counter

phs = mod(phs + floor(freq / 2 ^ 16), 2 ^ 16);

ref = phs < 32768;

% Get the next digital value (0 or 1) of the signal to track

sig = tracksig(it);

% Implement the phase-frequency detector

rst = ~ (qsig & qref); % Reset the "flip-flop" of the phase-frequency

% detector when both signal and reference are high

qsig = (qsig | (sig & ~ lsig)) & rst; % Trigger signal flip-flop and leading edge of signal

qref = (qref | (ref & ~ lref)) & rst; % Trigger reference flip-flop on leading edge of reference

lref = ref; lsig = sig; % Store these values for next iteration (for edge detection)

ersig = qref - qsig; % Compute the error signal (whether frequency should increase or decrease)

% Error signal is given by one or the other flip flop signal

% Implement a pole-zero filter by proportional and derivative input to frequency

filtered_ersig = ersig + (ersig - lersig) * deriv;

% Keep error signal for proportional output

lersig = ersig;

% Integrate VCO frequency using the error signal

freq = freq - 2 ^ 16 * filtered_ersig * prop;

% Frequency is tracked as a fixed-point binary fraction

% Store the current VCO frequency

vcofreq(1, it) = freq / 2 ^ 16;

% Store the error signal to show whether signal or reference is higher frequency

ervec(1, it) = ersig;

end

Neste exemplo, presume -se que um array trackig contém um sinal de referência a ser rastreado. O oscilador é implementado por um contador, com o bit mais significativo do contador indicando o status ligado / desligado do oscilador. Este código simula os dois flip-flops do tipo D que compõem um comparador de frequência de fase. Quando a referência ou o sinal tem uma borda positiva, o flip-flop correspondente muda para alto. Uma vez que a referência e o sinal estão altos, os dois flip-flops são reinicializados. Qual flip-flop é alto determina naquele instante se a referência ou sinal lidera o outro. O sinal de erro é a diferença entre esses dois valores de flip-flop. O filtro de pólo zero é implementado adicionando o sinal de erro e sua derivada ao sinal de erro filtrado. Este, por sua vez, é integrado para encontrar a frequência do oscilador.

Na prática, é provável que outras operações sejam inseridas no feedback desse loop de bloqueio de fase. Por exemplo, se o loop de bloqueio de fase implementasse um multiplicador de frequência, o sinal do oscilador poderia ser dividido em frequência antes de ser comparado ao sinal de referência.

Veja também

- Loop de frequência bloqueado

- Loop de bloqueio de fase da bomba de carga

- Recuperação de operadora

- Mapa de círculo - Um modelo matemático simples do loop de bloqueio de fase que mostra tanto o bloqueio de modo quanto o comportamento caótico.

- Costas loop

- Loop bloqueado por atraso (DLL)

- Receptor de conversão direta

- Sintetizador digital direto

- Filtro de Kalman

- PLL multibit

- Shortt-Synchronome clock - Slave pendulum phase-locked to master (ca 1921)

Notas

Referências

Leitura adicional

- Banerjee, Dean (2006), PLL Performance, Simulation and Design Handbook (4ª ed.), National Semiconductor , arquivado do original em 2012-09-02 , recuperado em 2012-12-04.

- Best, RE (2003), Phase-locked Loops: Design, Simulation and Applications , McGraw-Hill, ISBN 0-07-141201-8

- de Bellescize, Henri (junho de 1932), "La réception Synchrone", L'Onde Electrique , 11 : 230-240

- Dorf, Richard C. (1993), The Electrical Engineering Handbook , Boca Raton: CRC Press, Bibcode : 1993eeh..book ..... D , ISBN 0-8493-0185-8

- Egan, William F. (1998), Phase-Lock Basics , John Wiley & Sons. (fornece scripts Matlab úteis para simulação)

- Egan, William F. (2000), Frequency Synthesis by Phase Lock (2ª ed.), John Wiley and Sons. (fornece scripts Matlab úteis para simulação)

- Gardner, Floyd M. (2005), Phaselock Techniques (3ª ed.), Wiley-Interscience, ISBN 978-0-471-43063-6

- Klapper, J .; Frankle, JT (1972), Phase-Locked and Frequency-Feedback Systems , Academic Press. (Demodulação FM)

- Kundert, Ken (agosto de 2006), Predicting the Phase Noise and Jitter of PLL-Based Frequency Synthesizers (PDF) (4g ed.), Designer's Guide Consulting, Inc.

- Liu, Mingliang (21 de fevereiro de 2006), Build a 1.5-V 2.4-GHz CMOS PLL , Wireless Net Design Line, arquivado do original em 1 de julho de 2010. Um artigo sobre como projetar um IC PLL padrão para aplicativos Bluetooth.

- Wolaver, Dan H. (1991), Phase-Locked Loop Circuit Design , Prentice Hall, ISBN 0-13-662743-9

links externos

- Phase locked loop primer - Inclui vídeo integrado

- O Excel Unusual hospeda um modelo PLL animado e os tutoriais para codificar tal modelo .

![{\ displaystyle {\ begin {align} {\ dot {x}} & = - {\ frac {1} {RC}} x + {\ frac {1} {RC}} A_ {1} A_ {2} \ sin (\ theta _ {1} (t)) \ cos (\ theta _ {2} (t)), \\ [6pt] {\ ponto {\ theta}} _ {2} & = \ omega _ {\ text {free}} + g_ {v} (c ^ {*} x) \ end {alinhado}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/7aa30f8d69878ef11010da5b8a238c9811b425c7)

![{\ begin {align} {\ dot x} & = - {\ frac {1} {RC}} x + {\ frac {1} {RC}} {\ frac {A_ {1} A_ {2}} {2 }} \ sin (\ theta _ {{\ Delta}}), \\ [6pt] {\ dot \ theta} _ {{\ Delta}} & = \ omega _ {{\ Delta}} - g_ {v} (c ^ {{*}} x). \ end {alinhado}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/a27dc4e09c9f27ca06eda5c20cfd62db61852aa9)

![{\ begin {align} x & = {\ frac {{\ dot \ theta} _ {2} - \ omega _ {2}} {g_ {v} c ^ {*}}} = {\ frac {\ omega _ {1} - {\ dot \ theta} _ {{\ Delta}} - \ omega _ {2}} {g_ {v} c ^ {*}}}, \\ [6pt] {\ dot x} & = {\ frac {{\ ddot \ theta} _ {2}} {g_ {v} c ^ {*}}}, \\ [6pt] \ theta _ {1} & = \ omega _ {1} t + \ Psi , \\ [6pt] \ theta _ {{\ Delta}} & = \ theta _ {1} - \ theta _ {2}, \\ [6pt] {\ dot \ theta} _ {{\ Delta}} & = {\ dot \ theta} _ {1} - {\ dot \ theta} _ {2} = \ omega _ {1} - {\ dot \ theta} _ {2}, \\ [6pt] & {\ frac {1} {g_ {v} c ^ {*}}} {\ ddot \ theta} _ {{\ Delta}} - {\ frac {1} {g_ {v} c ^ {*} RC}} {\ ponto \ theta} _ {{\ Delta}} - {\ frac {A_ {1} A_ {2}} {2RC}} \ sin \ theta _ {{\ Delta}} = {\ frac {\ omega _ {2 } - \ omega _ {1}} {g_ {v} c ^ {*} RC}}. \ end {alinhado}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/e270e7df2f932355fbcf2a304ac607c0247b75f7)